新智元报道

新智元报道

【新智元导读】南大AI学院钱超教授团队,荣获EDA顶会2025最佳论文奖!其中,论文一作、四作、五作都是南大人工智能学院的本硕博生。芯片设计领域的传统难题——如何为多达百亿量级晶体管设计最优布局,从此有了一种巧妙的全新方法。

据南京大学人工智能学院网站报道,南大LAMDA组钱超教授团队在DATE 2025发表的芯片设计优化论文「Timing-Driven Global Placement by Efficient Critical Path Extraction」获会议最佳论文奖。

电子设计自动化(Electronic Design Automation,EDA)是芯片设计的基石产业,被誉为「芯片之母」。

欧洲设计自动化与测试会议(Design, Automation and Test in Europe Conference,DATE)是EDA领域的顶级国际学术会议。

本次DATE 2025最佳论文第一作者侍昀琦、第四作者林熙、第五作者薛轲分别是南京大学人工智能学院的硕士生、本科生和博士生,钱超教授为通讯作者,论文与华为诺亚方舟实验室合作完成。

开源:https://github.com/lamda-bbo/Efficient-TDP

在芯片设计领域,为多达百亿量级晶体管设计最优布局,一直是一个难解的技术难题。传统的布局方法要么选择快速但不够精准的网线加权方案,要么采用精确但运算量巨大的路径优化方法。

就像在一个拥挤的城市规划新的交通路线,既要考虑道路长度,又要确保交通畅通,面临精度与效率、局部与整体的冲突。这个两难困境一直困扰着芯片设计行业。

该论文提出了一种全新的时序驱动布局方法,巧妙地将效率和精度统一起来:

-

经典开源时序分析工具OpenTimer 使用O(n^2)复杂度的算法提取top-n条时序违例路径,且不支持基于违例端点的路径分析。该论文针对每个违例端点提取其top-n条违例路径,不仅能覆盖所有时序违例端点,还将提取n条违例路径的复杂度降至O(n),在时序分析中能够实现6倍加速。这个创新方法的核心在于「智能关键路径提取」技术,它能够快速定位需要优化的关键路径,将分析速度提升了6倍。 -

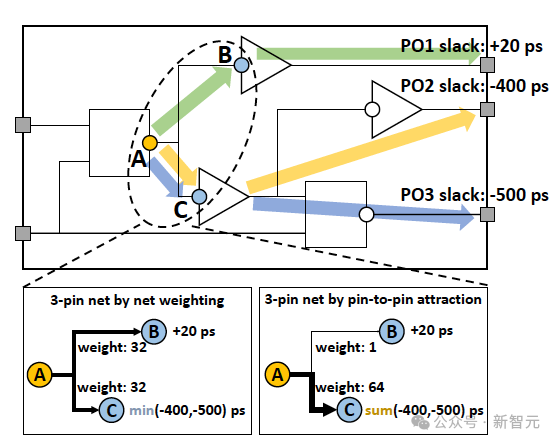

传统的基于线网的加权方案对于高扇出线网经常带来不必要的权重,从而过度优化许多不涉及时序违例的路径。论文提出了基于引脚间吸引力的精确指标,通过精确捕捉时序违例路径上的引脚对来建模时序信息,在显著提升时序指标的同时,几乎不造成整体线长的损失。 -

常用的时序模型RC Delay Model中,线网延时与其长度的平方成正比。论文首次提出将引脚间欧式距离的平方作为损失函数,并在GPU上实现了前向、反向传播的加速。较以往常用损失函数,在关键时序指标TNS和WNS上分别提升50%和30%。

图1:基于引脚间吸引力的时序目标建模

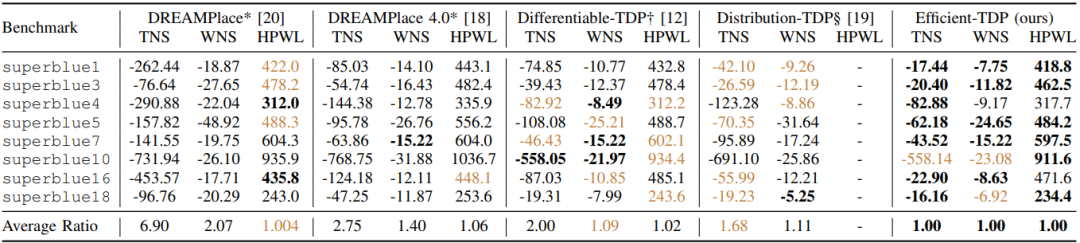

论文在ICCAD-2015竞赛数据集上进行了广泛的对比,相较于最先进的开源布局算法DREAMPlace 4.0做到了全部8个芯片的显著领先,特别是在TNS指标上达到60%的平均提升。

相较于SOTA方法Differentiable-TDP和Distribution-TDP算法分别达到50%和40.5%的TNS平均提升。

图2:时序和线长指标的实验结果

审稿人高度评价该工作,称「结果令人印象非常深刻,超过了所有先进工作」(「The results are very impressive, outperforming all state-of-the-art works」),取得显著提升(「significant improvements」)。

DATE自1994年创办以来已举办31届,今年将于3月31日至4月2日在法国里昂召开。DATE今年收到逾1200篇投稿,录用率约25%,共评选出4篇最佳论文奖(获奖率仅0.3%)。

近期,AI技术在芯片设计中的应用受到了国际上高度关注。Google在Nature提出AlphaChip,应用于TPU设计,而多家EDA头部厂商也推出了AI赋能的EDA产品。芯片设计流程冗长复杂,存在大量复杂优化问题。

作为人工智能的重要研究分支,演化算法受达尔文进化论启发,通过模拟「交叉变异」和「自然选择」行为,可用于求解机器学习中复杂优化问题,但这类算法几乎纯粹是「启发式」:在不少情况下有效, 但为何奏效、在何种条件下奏效却并不清楚。

LAMDA组周志华教授带领俞扬教授和钱超教授长期努力,希望能够建立起相应理论基础,并对算法设计给出指导;2019年他们在Springer出版专著《Evolutionary Learning: Advances in Theories and Algorithms》,总结了他们在该方向上过去二十年的主要工作,并于2021年出版中文版《演化学习:理论与算法进展》。

基于这些长期理论研究,LAMDA组近期针对芯片设计中的复杂优化问题设计出了多个原创领先算法,如:

-

针对芯片宏元件布局问题,该团队在NeurIPS’23发表的工作「Macro Placement by Wire-Mask-Guided Black-Box Optimization」较Google在Nature’21提出方法的布线长度缩短80%以上,并获得ACM SIGEVO Human-Competitive Results奖; -

针对芯片全局布局问题,该团队在DAC’24发表的Poster工作「Escaping Local Optima in Global Placement」通过变异算子缓解了当前解析式布局器易于陷入局部最优的问题,进一步提升芯片布线长度指标15%; -

针对芯片宏元件布局问题,该团队在NeurIPS’24发表的工作「Reinforcement Learning Policy as Macro Regulator Rather than Macro Placer」提出了新的基于强化学习的问题建模,通过训练策略对已有布局进行高效微调而不是从头摆放,保证了宏元件布局的贴边和规整,在时序和拥塞等指标上均取得了一致的显著提升; -

针对芯片宏元件布局问题,该团队在DAC’25发表的工作「ReMaP: Macro Placement by Recursively Prototyping and Periphery-Guided Relocating」将大量专家知识引入算法,优化了宏元件和标准元件的数据流,更加符合工业界的实际需求,较当前最先进的开源EDA工具OpenROAD的方法,提升芯片最终时序指标超65%; -

若干技术在华为海思落地验证,包括攻克华为「揭榜挂帅」难题「EDA专题难题:超高维空间多目标黑盒优化技术」,将芯片寄存器寻优效率平均提升22.14倍等。

LAMDA组目前与华为正在进一步合作攻关,希望通过先进芯片设计缓解当前先进制造工艺局限。

(文:新智元)